Paměťový subsystém: Dvakrát víc AGU a Load/Store

Intel teď odhalil architekturu svých nejnovějších procesorů Alder Lake. Tentokrát jsou to ale architektury dvě. Alder Lake je hybridní a vedle „velkých“ jader pro jednovláknový výkon má další „malá“ jádra Gracemont. Ta ale nejsou jen do počtu či pro úsporu energie v nečinnosti jako u ARMů v mobilech, naopak se významně podílí na celkovém výkonu. Jejich architektura je vlastně sama celkem velká a teď se na ní detailně podíváme.

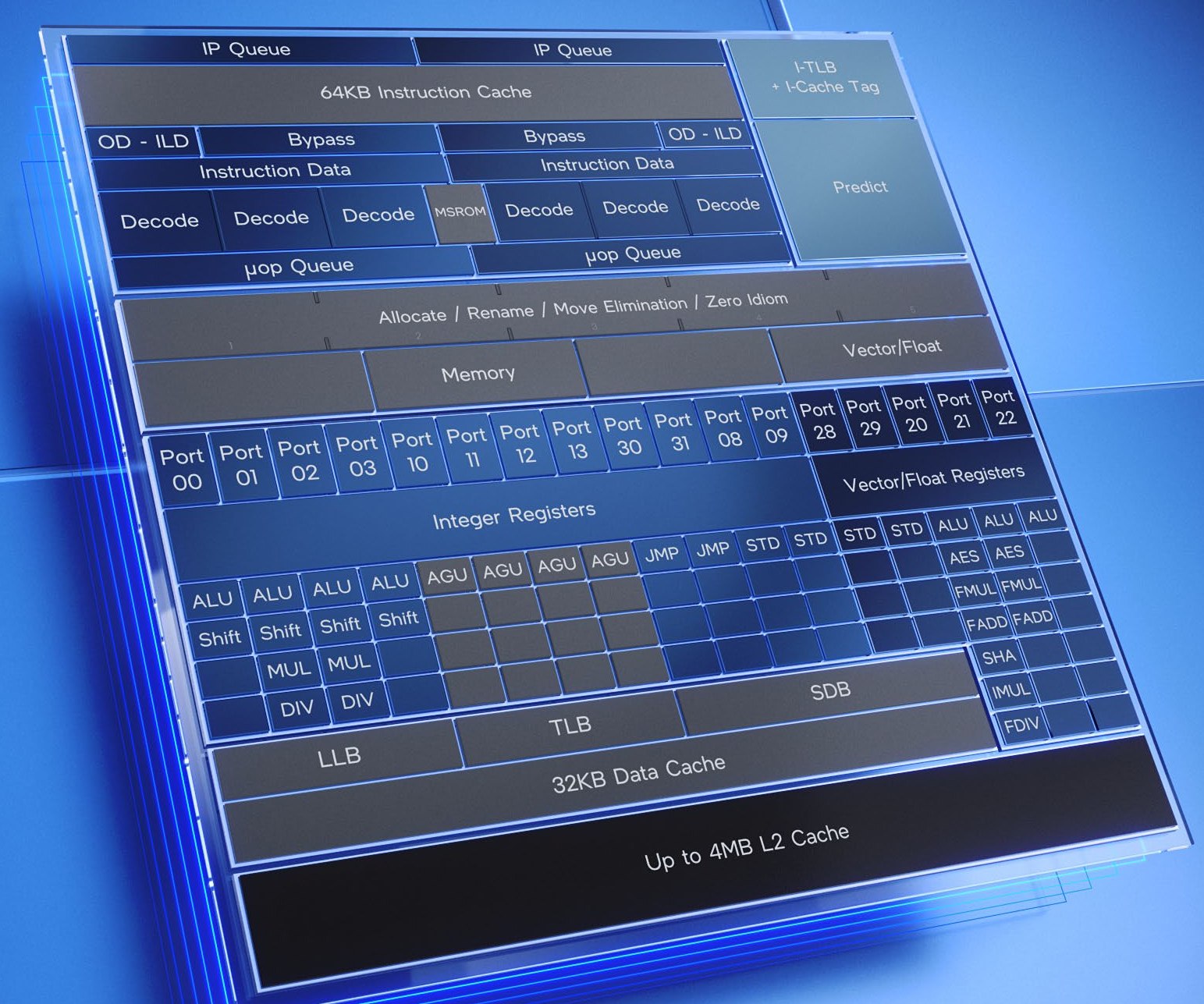

Load-Store část má čtyři jednotky AGU (porty 10, 11, 12, 13), které mohou provést dvě čtení a současně i dva zápisy dat do paměti (respektive do cache). Toto je na úrovni procesorů Ice Lake/Tiger Lake a dá se to považovat za velmi výkonný load/store subsystém. Tremont ještě měl jen dvě AGU, které uměly maximálně dvě operace za cyklus (maximálně dvě čtení nebo zápisy). Šířka těchto paměťových operací je 16 bajtů (128 bitů), což umožňuje za cyklus přečíst i zapsat data dvou SIMD vektorů instrukcí SSE, nebo jednoho 256bitového SIMD vektoru instrukcí AVX/AVX2 (32 B/cyklus).

V této datové propustnosti je jádro Gracemont horší než Golden Cove, jenž sice nezvládá o moc víc operací (3 čtení a 2 zápisy za cyklus), ale je to s dvojnásobnou datovou šířkou 256 bitů, takže propustnost je výrazně lepší (čtení až 96 bajtů/cyklus, zápis zřejmě 64 bajtů/cyklus), což se při náročných SIMD výpočtech s hodně daty může projevit. Na druhou stranu ani třeba Zen 3 také nemá zas tak silnou propustnost, takže toto nemusí typicky být tak velký handicap.

V Tremontu AGU byly univerzální, zatímco čtyři v Gracemontu jsou dedikované pro zápis nebo čtení. To znamená, že pokud program neustále současně zapisuje i čte, má Gracemont až 2× výkon těchto operací, ale pokud by se jen četlo nebo jen zapisovalo, není proti staršímu jádru rozdíl. Na dalších dvou portech (8, 9) jsou pak separátně operace pro ukládání dat.

Cache: sdílená L2 (a také L3)

L1 datová cache Gracemontu má kapacitu 32 KB, menší než je 48 KB v Golden Cove nebo Sunny/Willow/Cypress Cove (procesory Ice/Tiger/Rocket Lake), ale stejnou, jako má Zen 3. Jenže Gracemont také zřejmě má nižší (lepší) latenci. Pro operace „pointer-chasing“ Intel udává jen tři cykly. Je ale asi možné, že pro jiné operace už to budou čtyři cykly.

L2 Cache má u architektury Gracemont konfigurovatelnou kapacitu, může to být 2 MB, nebo 4 MB, což ale není pro jedno jádro, ale sdílené pro čtyři, která tvoří jeden sdružený klastr. Podle před časem uniklých informací by v procesorech Alder Lake měla být použitá kapacita nižší, 2 MB společně pro čtyři jádra.

Propustnost této cache je 64 bajtů za cyklus (1024 bitů/cyklus), což je relativně dost i pro zátěž všech jader, a její latence je 17 cyklů. L2 Cache také podporuje až 64 paralelních missů, tedy požadavků na data do L3 Cache nebo RAM (protože se v L2 nenašly). Toto zvyšuje výkon při prací s pamětí. Větší buffer těchto operací omezuje výskyt situací, kdy se musí čekat, až dorazí dříve požadovaná data, než se budou moci poptávat další.

Všechny úrovně cache v Gracemontu mají mít vylepšený prefetching, který detekuje různé druhy pravidelného streamování dat a dokáže pak podle onoho vzorce načítat předem z potřebných adres. Podporovaná je technologie Intel Resource Director, která umožňuje softwaru nastavit rozdělení pásma cache pro jednotlivá jádra nebo vlákna.

Zatímco L1 a L2 cache jsou přímo vlastnost architektury Gracemont, o L3 cache Intel zatím nehovoří. V procesorech Alder Lake budou asi jak velká jádra, tak malá jádra mít sdílenou L3 cache o stejných parametrech, neboť ta je vázaná na prstencovou sběrnici, která jádra propojuje. Zdá se ale, že zatímco každé velké jádro má vlastní 3MB blok L3 cache, u jader Gracemont bude jeden takový blok sdílený současně pro celý klastr čtyř jader Gracemont (ostatně podobně jako bude sdílená L2 cache).

Článek pokračuje další kapitolou.

- Contents

- Velká a „malá“ jádra: proč vůbec?

- Gracemont: „malá“(?) architektura silná už jako Skylake

- Výpočetní jednotky: 17 portů, potenciál pro vysoké IPC

- Paměťový subsystém: Dvakrát víc AGU a Load/Store

- Rychlost: „Malé“ jádro má až dvě třetiny výkonu velkého