The controller powering most upcoming PCIe 5.0 SSD detailed

We are starting to see introductions of first PCI Express 5.0 SSDs, which will enable up to double the read and write speeds on AMD AM5 and Intel LGA 1700 platforms. Many or majority of these SSDs will be based on the Phison E26 controller (and often on Phison reference design and firmware). Its manufacturer has now unveiled its specs at Computex 2022, showing us what the new cutting-edge SSD for PCs will look like.

The Phison E26 (the longer designation is PS5026-E26) is the successor to the E16 and E18 controllers on which many of the PCIe 4.0 SSDs (and initially in the days of the E16, almost all of them) were based. The manufacturer appears to have again coordinated development and launch with the availability of PCIe 5.0 ×4 on the AMD platform, as it did in 2019 with PCIe 4.0 drives.

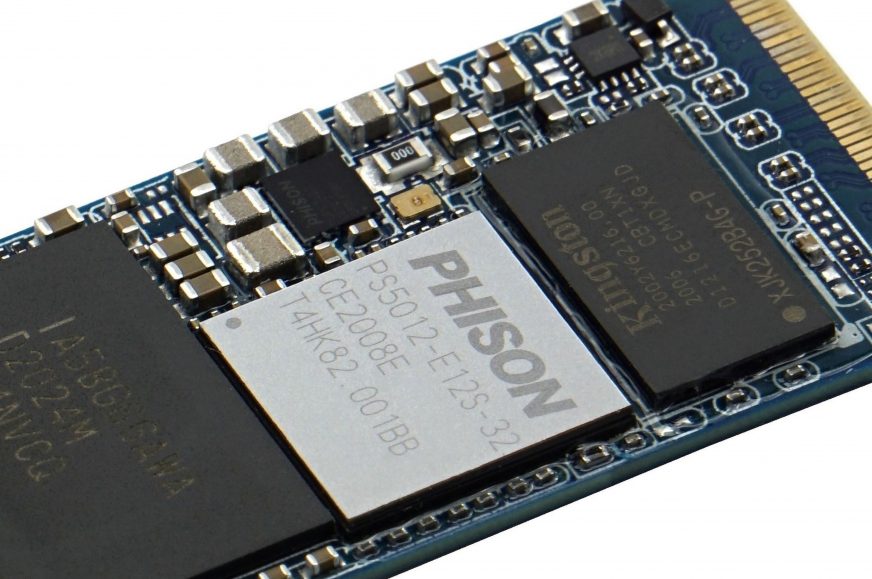

The Phison E26 is manufactured using the same 12nm TSMC process as the E18, but with the PCIe 5.0 ×4 interface, the number of contacts has increased (576 balls) and the chip package is larger, 16 × 16 mm (the E18 measured 12 × 12 mm, however the E16 was also 16 × 16 mm). Like its predecessors, the controller is eight-channel and supports up to 32 NAND chips in total. With this, therefore, it does not deviate from the standard of recent high-performance SSDs. Thus, it supports a capacity of M.2 modules up to 32 TB, which will probably not be needed during its career – in the consumer market such SSDs would be too expensive.

Special accelerators and the new generation of LDPC ECC

Other than the interface, where was the controller upgraded compared to the PCIe 4.0 generation of controllers? Read/write speeds to individual chips will now run at up to 2400 MT/s per channel, compared to 800 MT/s for the E16 and 1600 MT/s for the E18 controller. This will enable higher sequential write and read speeds. The performance of the controller will be enhanced to handle these. Its core will contain two ARM Cortex-R5 cores, but in addition to these it will have three dedicated CoXProcessor units. These should accelerate demanding operations such as ECC algorithms. The E18 controller had three Cortex-R5 cores without accelerators, but this new combination should be more powerful (up to twice as much performance) and also better in terms of power draw thanks to the accelerators.

Phison also states that the E26 will use a new ECC algorithm technology, it is supposed to be a fifth generation LDPC, whereas the Phison E16 and E18 were fourth generation. The new algorithm could probably improve performance, but it will also probably be more effective in correcting errors in the signal, so it will extend the life of TLC NAND (possibly also QLC NAND, which probably won’t be used in higher performance SSDs though).

The controller will also support the NVMe 2.0 protocol, whereas previous controllers were only capable of NVMe 1.3 and 1.4, respectively. It is also designed to meet the TCG Opal 2.0 security standard and support AES 256, SHA 512 and RSA 4096 hardware cryptography. It will also support slightly faster memory as DRAM cache – SSDs can use up to DDR4-3200 or LPDDR4-3200 chips.

Expected performance

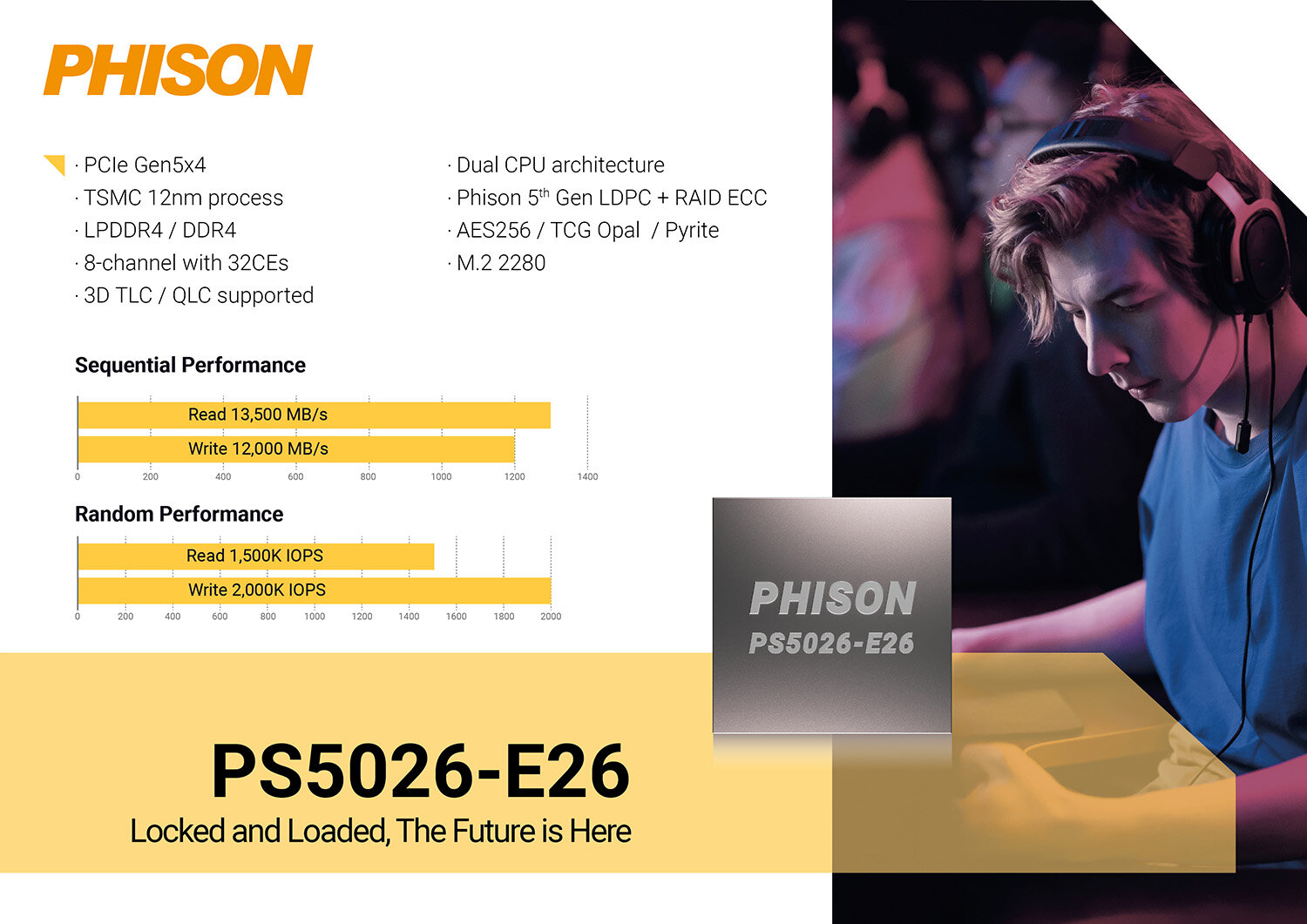

Roughly what performance will be achieved with this controller is indicated by the parameters given by Phison for reference implementations. Sequential reads are expected to be up to 13,500 MB/s, which could leave additional room for about 1,000 to 1,500 MB/s before reaching the limits of the PCI Express 5.0 ×4 interface.

This first implementation will therefore exploit quite a large part of the potential of PCIe 5.0, unlike the first generation of controllers for PCIe 4.0 (Phison E12 reached only 5000 MB/s leaving a lot at the table, as the second generation E18 reached 7400 MB/s). It is possible that the performance of the E26 controller will be improved a bit more later in future revisions and firmware updates, possibly in combination with future higher performance NAND chips.

Sequential writing is supposed to be slightly lower, up to 12 000 MB/s, which is, however, writing to the SLC cache. The sustainable write speed will probably depend a lot on the characteristics of the NAND chips, but it will be lower in any case.

Interestingly, the performance in random access is supposed to increase a lot too. Random reads are supposed to go up by 50 %. While for E18 the company typically claimed 1,000,000 IOPS, for PCIe 5.0 modules with Phison E26 it is supposed to be up to 1,500,000 IOPS. Random writes could be even faster, going from one million to 2,000,000 IOPS (this is the figure for writing to the pseudoSLC cache).

Tip: First PCIe 5.0×4 SSD announced: NVMe modules from Apacer and Zadak

SSD availability in autumn

Drives, or better said M.2 modules and in some cases PCIe 5.0 ×4 cards with these controllers should appear in stores in autumn. That means around the same time as the Ryzen 7000 processors and AM5 chipset boards.

It looks like the first generation of PCIe 5.0 SSDs with the Phison E26 controller will be based on 3D NAND of the TLC type from Micron, which was also cited as a development partner by AMD. Later on, however, there may be drives using NAND from Toshiba/Kioxia and others.

Micron may also be preparing its own SSDs with the Phison E26 controller, which would come to market under the Crucial brand. This would be a change from the past when Micron used its own controllers, but the flip side was that the company’s SSDs were a very late comers to the PCI Express 4.0 party, for example. With this change, maybe Micron or Crucial could release PCIe 5.0 SSDs much faster and actually in the first wave of products, thanks to the use of Phison E26.

Source: ComputerBase

English translation and edit by Jozef Dudáš, original text by Jan Olšan, editor for Cnews.cz

⠀